# 回路基板上の伝送路と電源パターンのEMIへの影響

Influence on EMI by the strip line, ground plane and power-supply plane on PCB

大力 賢次\* 輕部 俊幸\*\* 宮下 純一\*\* 蜜澤 雅之\*\*

#### 1.はじめに

EMI規制が本格化し,電子機器の高速化が進む中,プリント基板からのノイズ低減が望まれており,プリント回路基板のノイズ低減を目標とし,様々な試みがなされ,報告されている[1][2]。

現実に実施している対策として,基板の多層化,ノイズ対策素子の多用があるが,いずれもコストが増加する等の問題がある。そこで,パターン設計によるノイズ低減技術に注目が集まりつつある。これにはパターン設計の工夫によるノイズ低減,信号線の配線・部品配置・電源パターン(電源(Vcc)及びグラウンド(GND)層)の影響を考慮したもの等幾つかの手法がある。

我々は,この中で電源パターンのEMIへの影響に注目した。これまでにグラウンド(GND)面上のスリットの有無及びその大きさの変化がEMIへ及ぼす影響についての研究を実施し,報告を行った[3]。

ここでは,上記により得た結果に基づいて,平成10年度から実施している,長野県精密工業試験場と茨城県工業技術センターの共同研究テーマ「プリント配線板の電磁界分布とノイズ低減設計の研究」において実施した,よりシンプルにした回路基板上の伝送路と電源パターンが,EMIへ及ぼす影響についての結果[4]を報告する。

# 2.研究の目的

前項にも述べたが、電源パターンがEMIへ及ぼす影響は無視できるレベルではない。このことは、Vcc・GND 各層の設計次第で、部品の増加(コストの増加)無しにノイズ低減が可能であることを示唆している。また、一般的にノイズ対策に有効であるといわれている電源パターンのベタ化についても、条件次第でその効果が変化することを示す。

そこで,ノイズ電流を解析することによりVcc・GND パターンのEMI における最適化設計を実施できれば,設計段階での低コストなノイズ低減が実現可能である。

このような技術を確立するための基礎研究として、プリント配線板の電流・電磁界の分布を解析して、それらの解析結果とEMIの関係を明確にし、パターン設計時におけるノイズ低減技術の確立を目指すために本研究を実施する。

## 3.簡単なこれまでの結果

グラウンド面のスリットはその位置によりEMIへ の影響が異なる

伝送路直下のスリットはEMIレベル(放射電界強度)を強める。

上記のようなスリットがEMIへ影響を及ぼす原因 についての考察

- ・帰還電流の迂回によるもの。

- ・伝送路インピーダンスの不整合。

・伝送路を給電点としたスリットによる電源パターンの励振。

伝送路直下にあるスリットの垂直方向への大きさの変化によるEMIへの影響。

・スリットの大きさの変化とEMIへの影響について, 比例傾向は現れたが,明確な確認はできなかった。

上記のような実験結果より,ICを実装した基板を使用した実験での限界(要因が多すぎ相互影響により明確な結果が見えない)が生じた。

そこで,信号発生器(SG)を使用し電源パターン,電送線路のインピーダンス等を考慮しEMIとの関係を解析することとした。

#### 4.実 験

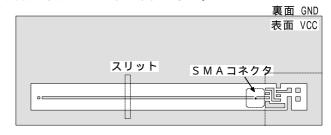

実験に使用した基板はインピーダンス50 全長200 mmのストリップラインを有する。これをICの入力を想定した6pFのコンデンサで終端した。外形は100ラ280 mm, 裏面はベタグラウンド(GND)である。

この基板のGND層(裏面)に、図のような外形5540 cm の長方形のスリットを設けたもの、基板長を変化させたもの、伝送路長を変化させたもの、及びVcc層・GND 層をはぎ取り面積を変化させたものを作製した。この基板にSG出力をSMAコネクタ部よりストリップラインに注入した状態で、近傍電磁界強度、放射電界強度、反射特性の測定を行った。使用した基板材質はガラスエポキシ(=3.5)である。

実験に使用した基板を図1に示す。

図1 実験回路基板

実験の内容は放射電界強度測定(EMI測定),近傍磁界 測定(基板の電流分布の測定),伝送線路の反射特性 (S11)測定である。

放射電磁界測定は3m法の暗室において実施した。また,近傍磁界測定はEMSCANにより測定を行った。反射特性測定はネットワークアナライザを使用した。

#### 5.実験結果及び考察

#### 5.1 電源パターンのEMIへの影響

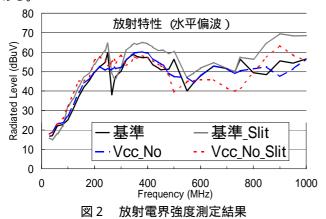

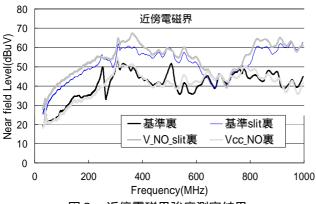

電源パターンの変化とEMIの関係を検討するために,放射電界強度及び近傍電磁界強度の測定を実施した。結果の一例をそれぞれ図2,図3に示す。

図2は,伝送路を上向きにした測定距離3mでの水平偏波,放射電界強度測定結果(EMI測定結果)である。なお,ターンテーブルは360度回転させたデータである。

図中の " 基準ライン " は基準となる加工していない基板のデータ ," Vcc\_No" は基板のVcc層をはぎとった物のデータである。また , それぞれの基板のグラウンド面に図1に示すような , スリットを開けた状態での基板による測定結果が " 基準 Slit"," Vcc No Slit"である。

図3は、EMSCANによる基板裏側(GND面)の近傍電磁界強度の測定結果である。図2と同様に基準基板と、Vccをはがした基板の、スリットの有・無の状態での測定結果である。

図 3 近傍電磁界強度測定結果

これらの結果より以下のようなことが言える。

Vcc層をはいだ結果,共振現象が消滅した周波数帯が確認できた。これらの放射ピークはVcc-GND間若しくは伝送路-Vccの影響によると考えられる。これはEMIデータ並びに近傍電磁界データの双方で同一周波数にみられる。

近傍電磁界強度のGND層側測定結果と放射電界強度の 測定結果(周波数 - 電磁界強度)が非常に酷似している が,伝送線路からの結果とはその特徴が異なる。これに より,伝送線路からの電磁界放射よりも電源パターンか らの電磁解放射が,EMIに対する影響が大きいことが予 想できる。

スリットの有無による比較では,スリットの有無に影響されない周波数帯の存在や, Vcc層の有無に大きく影響する周波数帯の存在が明らかになった。

#### 5.2 電流分布測定

電源パターン上の電流分布を検討するために近傍磁界分布をEMSCANにより測定した。これにより基板の電源パターン上における高周波電流の流れを把握し、パターン設計のEMIに対する影響解明に活用する。

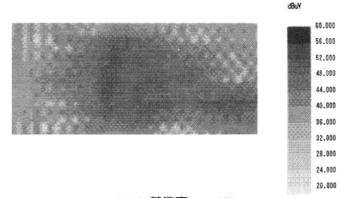

測定結果の一部を図4,図5に示す。

図4は253MHzにおける基板裏側(GND面)の近傍磁界の強度分布である。色の濃い部分ほど磁界が強い。(1)は基準基板,(2)はVcc層をはいだ基板での,同一条件での測定結果である。

図5は,グラウンド面にスリットを開けた基板の裏側 (GND面)のデータである。(1)が測定周波数120MHz,(2)は253MHzでの測定結果である。

電源パターンの電磁界測定結果より以下のようなことがいえる。

Vcc層の有無により、グラウンド面に現れる磁界強度が大きく変化している。この傾向はEMI測定結果と良く一致しており、電源パターンの共振現象によるEMIへの関与がわかる。

開口の周辺に帰還電流によると考えられる磁界が確認できる。しかしながら確認できない周波数領域の存在もあり、EMIに対する影響は帰還電流の変化による現象だけではない。

Vcc層における測定データの変化はほとんど現れない。 これは、伝送路を流れる電流による磁界が大きく支配的 だからである。

(1)基準裏 253MHz

56.000 52.000 48.000 44.000 40.000 36.000 32.000 28.000 24.000

dBu∀

60.000

(2) Vcc\_No裏 253MHz 図4 近傍磁界強度分布測定結果

(1) Slit裏 120MHz

20.000

(2) Slit裏 253MHz 図 5 近傍磁界強度分布測定結果 2

# 5.3 ネットワークアナライザによる

基板の反射特性測定結果

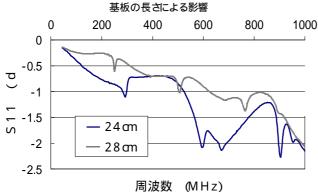

基板の共振現象を把握するためにネットワークアナライザにより(S11)の測定を行った。測定は基板長,伝送路長,基板幅等を変化させて実施した。

図 6 反射特性測定結果

実験の結果,基板の長さに依存した電源パターンの共振が確認できた。反射特性S11の測定結果を図6に示す。 図のように基板の長手方向に対する長さの変化により共振点が移動していることがわかる。

また、伝送線路とVcc層との距離の変化と、共振の深さが比例関係にあることも明らかになった。これらの現象は、基板上にICを実装した場合の実験でも同様の傾向を見せている。

### 6.まとめ

本実験に使用した形状の回路基板においては,電源パターンの形状・状態の違いがEMI放射に大きな影響を及ぼしていることが確認できた。

さらに以下のような点が確認できた。

電源パターンからの電磁界放射は基板長に寄与した 共振現象により強められる。

電源パターンの共振による電磁界放射は伝送路からの給電による。

電源パターン上のスリットが,共振を深くする要因となってEMIが悪化する。

このことから,GND面上のスリットがEMIへ及ぼす影響としては,帰還電流の経路変化による影響よりも,スリットを開けたことにより,伝送路が給電点となり,Vcc層やGND層を励振させることによる影響が大きく,この周波数は基板外形とVccとGNDとの結合状態に影響することが予測される。

今後は、上記の結果を基に理論解析による裏付けとその計算結果によるシミュレーションについての検討を実施する予定である。

## [参考文献]

- 1) 上,他:信学技報,EMCJ98-7(1998-04)

- 2) 渋谷,他:回路実装学会学術講演会, (24A-08,1998)

- 3) 大力,輕部他:信学会総合大会大会予稿集, (B-4-16,1998)

- 4) 大力,輕部他:信学会ソサイエティ大会大会予稿集, (B-4-28,1998)